#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

### Games in Open Systems Verification and Synthesis

by

Yiu-Chung Mang

M. Eng. (Oxford University, England) 1995

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Thomas A. Henzinger. Chair

Professor Robert K. Brayton

Professor John Steel

Spring 2002

**UMI Number: 3063469**

#### UMI Microform 3063469

Copyright 2002 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### Games in Open Systems Verification and Synthesis

Copyright 2002 by Yiu-Chung Mang

#### Abstract

Games in Open Systems Verification and Synthesis

bv

Yiu-Chung Mang

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Thomas A. Henzinger, Chair

This dissertation investigates game-theoretic approaches to the algorithmic analysis of concurrent, reactive systems. A concurrent system comprises a number of components working concurrently; a reactive system maintains an ongoing interaction with its environment. Traditional approaches to the formal analysis of concurrent reactive systems usually view the system as an unstructured state-transition graphs; instead, we view them as collections of interacting components, where each one is an open system which accepts inputs from the other components. The interactions among the components are naturally modeled as games.

Adopting this game-theoretic view, we study three related problems pertaining to the verification and synthesis of systems. Firstly, we propose two novel game-theoretic techniques for the model-checking of concurrent reactive systems, and improve the performance of model-checking. The first technique discovers an error as soon as it cannot be prevented, which can be long before it actually occurs. This technique is based on the key observation that "unpreventability" is a local property to a module: an error is unpreventable in a module state if no environment can prevent it. The second technique attempts to decompose a model-checking proof into smaller proof obligations by constructing abstract modules automatically, using reachability and "unpreventability" information about the concrete modules. Three increasingly powerful proof decomposition rules are proposed and we show that in practice, the resulting abstract modules are often significantly smaller than the concrete modules and can drastically reduce the space and time requirements for verification. Both techniques fall into the category of compositional reasoning.

Secondly, we investigate the composition and control of synchronous systems. An essential property of synchronous systems for compositional reasoning is non-blocking. In the composition of synchronous systems, however, due to circular causal dependency of input and output signals, non-blocking is not always guaranteed. Blocking compositions of systems can be ruled out semantically, by insisting on the existence of certain fixed points, or syntactically, by equipping systems with types, which make the dependencies between input and output signals transparent. We characterize various typing mechanisms in gametheoretic terms, and study their effects on the controller synthesis problem. We show that our typing systems are general enough to capture interesting real-life synchronous systems such as all delay-insensitive digital circuits. We then study their corresponding singlestep control problems — a restricted form of controller synthesis problem whose solutions can be iterated in appropriate manners to solve all LTL controller synthesis problems. We also consider versions of the controller synthesis problem in which the type of the controller is given. We show that the solution of these fixed-type control problems requires the evaluation of partially ordered (Henkin) quantifiers on boolean formulas, and is therefore harder (nondeterministic exponential time) than more traditional control questions.

Thirdly, we study the synthesis of a class of open systems, namely, uninitialized state machines. The sequential synthesis problem, which is closely related to Church's solvability problem, asks, given a specification in the form of a binary relation between input and output streams, for the construction of a finite-state stream transducer that converts inputs to appropriate outputs. For efficiency reasons, practical sequential hardware is often designed to operate without prior initialization. Such hardware designs can be modeled by uninitialized state machines, which are required to satisfy their specification if started from any state. We solve the sequential synthesis problem for uninitialized systems, that is, we construct uninitialized finite-state stream transducers. We consider specifications given by LTL formulas, deterministic, nondeterministic, universal, and alternating Büchi automata. We solve this uninitialized synthesis problem by reducing it to the well-understood initialized synthesis problem. While our solution is straightforward, it leads, for some specification formalisms, to upper bounds that are exponentially worse than the complexity of the corresponding initialized problems. However, we prove lower bounds to show that our simple solutions are optimal for all considered specification formalisms. The lower bound proofs require nontrivial generic reductions.

Professor Thomas A. Henzinger Dissertation Committee Chair to Wendy ...

# **Contents**

| List of Figures |      |         |                                                    | v  |

|-----------------|------|---------|----------------------------------------------------|----|

|                 |      |         |                                                    | vi |

| 1               | Intr | oducti  | on                                                 | 1  |

|                 | 1.1  | Backgr  | round                                              | 1  |

|                 |      | 1.1.1   | Verification and synthesis                         | 1  |

|                 |      | 1.1.2   | Open systems and Games                             | -1 |

|                 |      | 1.1.3   | Games in logic and concurrency theory              | 7  |

|                 | 1.2  | Thesis  | Overview                                           | 8  |

|                 |      | 1.2.1   | Early error detection in model-checking            | 9  |

|                 |      | 1.2.2   | Automatic assume-guarantee proof decomposition     | 10 |

|                 |      | 1.2.3   | The composition and control of synchronous systems | 10 |

|                 |      | 1.2.4   | Synthesis of uninitialized systems                 | 12 |

| 2               | Pre  | liminaı | ries                                               | 13 |

|                 | 2.1  | Modul   | les and composition                                | 13 |

|                 | 2.2  |         | ation                                              | 14 |

|                 |      | 2.2.1   | Specification: Linear-time temporal logic          | 14 |

|                 |      | 2.2.2   | Reachability and invariant verification            | 15 |

|                 |      | 2.2.3   | Single-step vs. multi-step verification            | 16 |

|                 | 2.3  | Contro  | ollability                                         | 17 |

| 3               | Ear  | ly Erro | or Detection                                       | 20 |

|                 | 3.1  | •       | luction                                            | 20 |

|                 | 3.2  |         | Detection of Invariant Violation                   | 24 |

|                 |      | 3.2.1   | Forward and backward state exploration             | 24 |

|                 |      | 3.2.2   | Controllability and early error detection          | 25 |

|                 | 3.3  | Lazv a  | and Constrained Controllability                    | 26 |

|                 |      | 3.3.1   | Lazy controllability                               | 27 |

|                 |      | 3.3.2   | Constrained controllability                        | 28 |

|                 | 3.4  | Exper   | iments                                             | 29 |

|                 |      | 3.4.1   | Demarcation protocol                               | 29 |

|                 |      | 3 1 2   | •                                                  | 30 |

CONTENTS iii

|   |     | 3.4.3  | Results on BDD sizes and discussion                   |

|---|-----|--------|-------------------------------------------------------|

|   | 3.5 |        | ed Controllability and Iterative Strengthening        |

|   |     | 3.5.1  | Bounded controllability                               |

|   |     | 3.5.2  | Iterative strengthening                               |

|   |     | 3.5.3  | Discussion                                            |

|   |     |        |                                                       |

| 4 | Aut |        | c Proof Decomposition                                 |

|   | 4.1 |        | uction                                                |

|   | 4.2 | Overvi | iew and Additional Definitions                        |

|   |     | 4.2.1  | Chapter Overview                                      |

|   |     | 4.2.2  | Additional Definitions                                |

|   | 4.3 | Modul  | lar Rules for Invariant Verification                  |

|   |     | 4.3.1  | Reachability-based abstractions                       |

|   |     | 4.3.2  | Controllability and reachability-based abstractions   |

|   | 4.4 | Implei | mentation of the Verification Rules                   |

|   | 4.5 | Exper  | imental Results                                       |

|   |     | 4.5.1  | Demarcation protocol                                  |

|   |     | 4.5.2  | Token ring arbiter                                    |

|   |     | 4.5.3  | Sliding window protocol                               |

|   |     | 4.5.4  | Discussion                                            |

| _ | _   | • • •  |                                                       |

| 5 |     | -      | ion and Control                                       |

|   | 5.1 |        | luction                                               |

|   | 5.2 |        | for Synchronous Composition                           |

|   |     | 5.2.1  | Asynchronous modules                                  |

|   |     | 5.2.2  | Moore modules                                         |

|   |     | 5.2.3  | Statically typed modules (or Reactive Modules [AH99]) |

|   |     | 5.2.4  | Dynamically typed modules                             |

|   |     | 5.2.5  | Dependent type modules                                |

|   |     | 5.2.6  | Summary of types                                      |

|   | 5.3 |        | cation: Constructive Semantics                        |

|   |     | 5.3.1  | Boolean circuits                                      |

|   |     | 5.3.2  | Constructive operational semantics                    |

|   |     | 5.3.3  | From boolean circuits to modules                      |

|   | 5.4 |        | ped and Typed Control Problems                        |

|   | 5.5 | Algor  | ithms and Complexity of Control                       |

|   |     | 5.5.1  | Asynchronous control                                  |

|   |     | 5.5.2  | Moore control                                         |

|   |     | 5.5.3  | Statically typed control                              |

|   |     | 5.5.4  | Dynamically typed control                             |

|   |     | 5.5.5  | Dependent type control                                |

|   |     | 5.5.6  | Unrestricted control                                  |

|   |     | 5.5.7  | The relative power of controllers                     |

CONTENTS

| 6                                     | Synthesis of Uninitialized Systems |                                         |    |  |  |  |  |

|---------------------------------------|------------------------------------|-----------------------------------------|----|--|--|--|--|

|                                       | 6.1                                | Preliminaries                           | 88 |  |  |  |  |

|                                       | 6.2                                | The Uninitialized Realizability Problem | 89 |  |  |  |  |

|                                       |                                    | 6.2.1 Reducing URP to RP                | 9( |  |  |  |  |

|                                       |                                    | 6.2.2 Constructing always (R)           | 9  |  |  |  |  |

|                                       |                                    | 6.2.3 URP Complexity                    | 9: |  |  |  |  |

| · · · · · · · · · · · · · · · · · · · |                                    | Uninitialized Specifications            | 99 |  |  |  |  |

| Bi                                    | bliog                              | raphy 1                                 | 03 |  |  |  |  |

# List of Figures

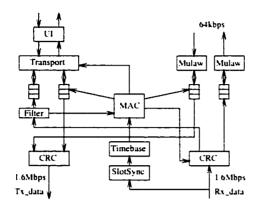

| 3.1 | The TCI protocol stack and the number of iterations of global state exploration to discover the error                                                              | 31 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

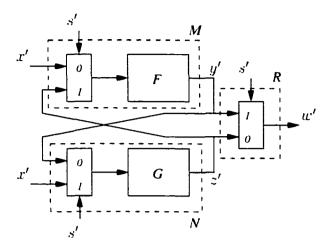

| 5.1 | A cyclic circuit composed of three modules $P$ , $Q$ , and $R$ . It performs the following function: if $s'$ then $w' = F(G(x'))$ else $w' = G(F(x'))$ , where $F$ |    |

|     | and $G$ are two combinational blocks, such as a shifter and adder. $\dots$                                                                                         | 66 |

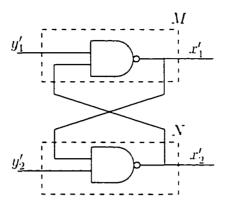

| 5.2 | A latch implemented as two NAND gates                                                                                                                              | 68 |

# List of Tables

| 3.1 | Number of iterations required in global state exploration to find errors in 3 models of the demarcation protocol. The errors are e1e4. The columns are L (lazy controllability). C (constrained controllability). R (regular con-                                                                                                                                                                                                                 |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | trollability), and G (traditional global state exploration) Average maximum number of BDD nodes required for error detection during the controllability (Control) and reachability computation (Total) phases.                                                                                                                                                                                                                                    | 30 |

|     | Dynamic variable ordering was turned off in (a) and (b), and on in (c) and (d). The results are given for lazy controllability and global state exploration. All data are in thousands of BDD nodes, and the standard deviations are                                                                                                                                                                                                              |    |

|     | given in parenthesis                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

| 4.1 | Experiment results on the demarcation protocol                                                                                                                                                                                                                                                                                                                                                                                                    | 52 |

| 4.2 | Experiment results on the token-ring arbiter                                                                                                                                                                                                                                                                                                                                                                                                      | 5. |

| 4.3 | Experiment reults on the sliding window protocol                                                                                                                                                                                                                                                                                                                                                                                                  | 5- |

| 5.1 | (a) Complexity of composability checking, as well as single-step and multi-<br>step control for the various module classes. For statically and dynamically<br>typed modules, we consider both arbitrary and fixed controller types. The<br>quantity $n$ is the size of the module description. Each problem is complete<br>for the corresponding complexity class. (b) Existence of most state-general<br>(MSC) and most general (MC) are tables. | -, |

|     | (MSG) and most general (MG) controllers                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

| 6.1 | The cost of moving from $R$ to $always(R)$                                                                                                                                                                                                                                                                                                                                                                                                        | 9: |

| 6.2 | The complexity of the RP_HRP_and HSP                                                                                                                                                                                                                                                                                                                                                                                                              | 10 |

#### Acknowledgments

I would like to express my sincere gratitude towards my advisor Prof. Thomas A. Henzinger. I thank him for his generous financial support: for teaching me everything necessary to carry out research work: for his vision and inspiration on the future of formal methods: and for his patience and encouragement during the ups and downs of my entire graduate life.

My gratitude also goes to Luca de Alfaro. We spent many hours working on various research problems: in fact, most results presented in this dissertation were obtained in collaboration with him. He is quick, and is always enthusiastic about every idea. Luca is also a very good friend: He introduced me to photography and Italian cooking. It is wonderful to be able to work with him.

A large portion of the first half of my graduate life went to the development of the model-checker Mocha, a joint effort with Shaz Qadeer and Sriram Rajamani. It is a great experience working with them. Developing a large software system is a huge undertaking: without them, it would not be possible to have this tool for conducting all the experiments in this dissertation. I thank Sriram Krishnan and Orna Kupferman, whom I have been fortunate enough to work with on one of the problems presented in this dissertation. I also thank Rupak Majumdar and Jean-Francois Raskin for the fun when working on one of the papers.

I gained my first industrial experience on model-checking during my two summer internships at the Intel Strategic CAD Labs in Hillsboro. Oregon. I thank Pei-Hsin Ho for being my mentor at SCL. He taught me much about model-checking, and formal verification in general, from the industrial perspective.

My stay at Berkeley has been enjoyable. I thank all the members of the Berkeley CAD group for contributing to such an inspiring and pleasant research environment. I thank Michael Shilman for organizing the CAD picnic with me: Subarnarehka Sinha for sharing my burden (both physically and financially) in organizing the CAD seminar. I also thank her for listening patiently to all my grumble about life.

Finally, I am very grateful to my parents and Wendy, who have endured my pursuit of doctoral degree. A million words cannot express my gratitude towards them.

# Chapter 1

# Introduction

My work is a game, a very serious game.

- M.C. Escher (1898 - 1972)

### 1.1 Background

### 1.1.1 Verification and synthesis

This dissertation investigates game-theoretic approaches to the algorithmic analysis of concurrent reactive systems. A concurrent system comprises a number of components working concurrently: a reactive system maintains an ongoing interaction with its environment. Such systems abound in real-life: digital circuits, microprocessors, communication protocols, control of nuclear reactors, to name a few. Logical correctness in the design of such systems are of paramount importance: in the case of digital circuits and microprocessors, logical errors may result in loss of millions of dollars [Coe95]; in the case of nuclear reactors, loss of human lives. Hence, for decades, producing correct reactive systems have been the main subject among engineers and computer scientists. Formal methods have evolved to be one of the most prominent tools in the design of correct systems.

Correct systems can be designed by hand followed by verification: they can also be synthesized automatically from the specifications. In formal methods, both the systems and the specifications are given in some formal languages such as modal logic or automata that accept infinite words. In systems verification, the most widely used technique is extensive simulation. This technique serves as a good method to falsify the design; however, correctness can never be guaranteed. The second approach is based on deductive meth-

ods, including theorem proving (cf. [Gor88, Pau94]), term-rewriting (cf. [DJ89, Klo91]) and proof checking (cf. [DFH<sup>+</sup>93]). These techniques generally regard the systems as a set of axioms and attempt to prove that the specifications are theorems of these axioms. While these techniques, in principle, can handle arbitrary complicated designs, they often require much manual intervention and a great deal of training in mathematical logic.

The third approach to the verification of reactive systems is based on algorithmic methods. These include temporal-logic model-checking [QS81, CES86, VW94]) and refinement checking. In this approach, the systems are modeled as state-transition systems (Kripke structures), while the specifications can be specified in modal logic formulas,  $\omega$ -automata (automata that accepts infinite words) or even another state-transition system (in the case of refinement checking). The model-checking problem then asks, given a system and a specification, if the specification holds in the system. The refinement-checking problem(cf. [Raj99]), asks, given a system P (implementation) and a system Q (abstract specification), if the behaviors of P are included in the behaviors of Q. The most accepted notions of "inclusion" are trace-containment and simulation relation [Mil71]. In essence, both temporal-logic model-checking and refinement checking consist in exhaustive searches in the state-space of the state-transition systems and can be highly automated; hence they are well-suited for the automatic verification of finite-state system.

Popular modal logics for specifying nonterminating reactive systems include Linear Temporal Logic (LTL) [Pnu77]. Computation Tree Logic (CTL) [CE81, QS81] and modal  $\mu$ -calculus [Koz83]. LTL is a linear-time logic for expressing properties about linear, infinite computation traces generated from the state-transition systems. Its syntax has, in addition to atomic propositions and colean operators, a number of modal operators including  $\bigcirc \varphi$  ( $\varphi$  holds in the successor state).  $\square \varphi$  ( $\varphi$  holds in all subsequent states) and  $\varphi \mathcal{U} \psi$  ( $\varphi$  holds in the subsequent states until  $\psi$  holds), where  $\varphi$  and  $\psi$  are LTL formulas. On the other hand, CTL expresses properties about the infinite computation trees of the systems. It allows expression of universal as well as existential properties such as "from all states, there exists a path to the reset state." Unlike LTL, its modal operators are quantified by either the universal  $\forall$  (all successors) or the existential  $\exists$  (some successors) quantifier. The  $\mu$ -calculus is a modal logic for specifying properties of reactive systems modeled as Kripke structures. The syntax of propositional  $\mu$ -calculus consists of boolean operators and modalities including  $\forall \bigcirc$  (for all successors) and  $\exists \bigcirc$  (exists some successors), as well as the greatest and least fixpoint operators. Both LTL and CTL are fragments of  $\mu$ -calculus since the modal operators

and  $\mathcal{U}$  can both be encoded in  $\mu$ -calculus using fixpoints.

The main limiting factor in the algorithmic analysis of finite-state systems is the state-explosion problem; that is, the number of states to be explored can be exponential in the number of concurrent components in the system. To see this, consider a system P with m components, each having at most n states. Then the system P may have  $n^m$  states. In fact, for most popular system description languages, both temporal logic model-checking and refinement checking are known to be PSPACE-complete in the size of the description of the reactive systems [SC85, AH98]. To combat the state-explosion problem, a number of techniques have been proposed. For example, the symbolic techniques [McM93] represent the states and transitions of the systems implicitly using some succinct data structures, such as decision diagrams [Brv86] or boolean formulas [BCCZ99]: abstract interpretation [Dam96. GS97 abstracts away the nonessential part of the systems and therefore reduces the state space to be explored: compositional or modular verification attempts to prove the properties of a system by reasoning about behavior of the individual components. One notable example of compositional verification is assume-guarantee reasoning [Sta85, CLM89, AL95, AH99, McM97, HQR00]; the essential idea is to verify each component assuming the presence of a correct environment. This assumption will then be discharged by proving that it is an abstraction of the real environment.

Correct systems can also be synthesized from specifications. Automatic construction of correct systems has attracted much attention in several branches of engineering. For example, in Very Large Scale Integrated (VLSI) circuits where finite state machines constitute the basic building blocks of such circuits, the sequential synthesis problem asks, given a specification characterizing the set of permissible implementation, for the construction of a finite state machine M allowed by the specification such that M satisfies some optimality criteria [dM94]. In control theory, discrete-event systems (DES) [RW89] model the sequencing of events of dynamic systems, such as the arrival or departure of a customer in a queue, the start or completion of a task in an operating system, or the transmission or receipt of a packet in a communication system. The control problem of an DES P asks for synthesizing a controller C (or supervisor) such that the composed, closed-loop system  $P\|C$ , where  $\|$  denotes lock-step composition, meets certain safety criteria such as stability, mutual exclusion and data consistency. The control problem for DES is highly related to the synthesis problem, and they share much similarity in the formalisms and solutions.

Informally, the synthesis problem can be stated as follows: a stream requirement is

a specification on the input-output behavior of the synthesized system, and the realizability problem asks, given an specification  $\psi$  (expressed as modal logic formulas or  $\omega$ -automata) over sets of input and output signals, whether there exists a reactive system that assigns to every possible input sequence an output sequence so that the resulting computation satisfies  $\psi$ . If the answer is Yes, then the synthesis problem asks for the construction of such a system. The synthesis problem, closely related to Church's solvability problem [Chu62], was solved by Büchi and Landweber for stream requirement given as sequential calculus [BL69]. Since then, several algorithmic solutions have been proposed for other specification formalisms including LTL [ALW89, PR89a, PR89b], CTL [KMTV00] and  $\mu$ -calculus [KV00].

In general, the synthesis problem is harder than the verification problem. For finite-state systems, while LTL verification problem is in PSPACE, the LTL synthesis problem is 2EXPTIME-complete [PR89a]. One source of hardness, like verification, is the stateexplosion problem. Also, the synthesized systems are usually required to meet certain minimal behavior such as deadlock-freedom (nonblocking); that is, any finite trace of the synthesized system should always be extensible to a longer finite trace that belongs to the system. The nonblocking requirement is essential in several verification methodology such as assume-guarantee reasoning and simulation generation [KMP98]. In addition, synthesis of controllers often suffers from the observability problem [CDFV88, LW88b], in which some events of the system may not be observable by the controller. While the synthesis of a twocomponent system under partial observation (incomplete information) for LTL may incur exponential costs over that under complete information [RG95, Var95, KS97], the synthesis of a multi-component system (such as decentralized supervision [LW88a, LW90, RW92]) under incomplete information is in general undecidable [Rei84, PR90]. Practical remedies are often architectural in nature: they include hierarchical and modular synthesis [WW96] and various domain specific heuristics [Oku86, CL90, PRSV98].

#### 1.1.2 Open systems and Games

In verification, the inputs from the environment to a system are treated as part of the system, which assigns nondeterministic values to the inputs. We call these systems closed. In synthesis, however, systems are treated as open: they interact with their environments and cannot constrain their environments' behaviors. Hence, a stream transducer, an open-loop DES, and a component in a closed system are all open systems. Open systems

possess interesting properties such as realizability. Besides, researchers have proposed other properties related to open systems. We give some examples below.

Receptiveness [Dil89, AL93, GSSAL98]. Given a reactive system, specified by a set of safe computation traces and a set of live computations (typically, expressed by an LTL formula), the receptiveness problem is to determine whether every finite safe computation can be extended to an infinite live computation irrespective of the behavior the environment. Module checking [KV96]. Given an open system and a CTL formula  $\varphi$ , the module-checking problem is to determine if, no matter how the environment restricts the external choices, the system satisfies  $\varphi$ .

Well-formedness of component interfaces [dAH01a, dAH01b, CdAHM02]. Given an interface F specified as a state-transition system, where each transition of F are annotated with an input assumption, that is, a set of input signals that F accepts: and an output guarantee, that is a set of output signals that F outputs if the input assumption is satisfied. An error state of F is a state where the environment of F cannot produce an input that F accepts. The interface F is well-formed iff the error state is not reachable under some environment. Well-formedness is less restrictive than receptiveness, which requires F to accept all inputs under all environments, and it permits the reasoning about components that have bidirectional ports [CdAHM02].

Alternating temporal-logic [AHK97]. Given a Alternating temporal-logic (ATL) specification  $\varphi$  and a concurrent system  $P = P_1 || P_2$  comprising two interacting components (agents)  $P_1$  and  $P_2$ , the ATL verification problem asks if the system P satisfies the specification  $\varphi$ . Questions that one can asks in ATL include: Does the agent  $P_1$  (say, a processor in a multi-processor system) have a strategy to meet a requirement (say, the eventual ownership of the bus) no matter what the other agents (say, processors) do? Does the agent  $P_1$  (say, a traffic-light controller) have a strategy to avoid violation of some requirement (say, simultaneous green lights at an intersection) no matter what the other agents (say, vehicles on the road) do?

ATL extends the logic CTL: while CTL allows expression of universal and existential properties of closed systems. ATL also allows expression of adversarial and protagonist properties. The syntax of ATL generalizes the path quantifiers of CTL from  $\forall$  and  $\exists$  to  $\langle\!\langle P \rangle\!\rangle \varphi$  (P can ensure that, no matter what the environment of P does,  $\varphi$  holds), and  $[\![P]\!]\varphi$  (P cannot avoid  $\varphi$ ), where P is an open system. ATL has been applied in several areas of computer sciences such as correctness analysis of security protocols [KR00, KR01] and

feature interactions [CRS00].

All the stated problems arise from the interaction among the various components of the systems, and possess a game-like ( $\forall\exists$ ) interpretation: Does a solution exists no matter what the adversary (e.g. environment) does? This is in contrast to the closed system verification problem which asks for the solution of an  $\exists$  problem: for instance, does the system as a whole have a path to reach a bad state? Interactions among the open systems can be modeled as a game, while the participating systems are modeled as the players, and the specification modeled as the winning condition of the game. Then, solving the above stated problems amounts to solving the game, that is, deciding the winner of the game.

We adopt this game-theoretic view of systems in reasoning about complex systems that consists of components: often this view gives new insights in devising new model-checking algorithms. As an example, if one proves that a component P has a strategy to reach a goal no matter what its environment does, then the system P||Q consisting of P and Q has a path to reach that goal. As a result, there is no need to compute the composition of the components, and state-explosion can be avoided. In this dissertation, we study ways to improve the efficiency and capacity of LTL symbolic model-checking of closed, reactive systems, by reasoning about their components as open systems.

We are interested in the games arising from synchronous systems since they represent a large class of interesting and practical systems, such as electronic circuits. Solving the games arising from synchronous systems often require the solutions to the single-step games, which informally asks if the system or its environment can reach a specified goal (e.g. a specified state) in exactly one step. For example, consider the following multi-step, reachability game: Does the system have a strategy to reach a specified state s eventually. We can solve the problem by iteratively asking: Is the system already in the state s? Does the system have a strategy to reach s in one step? Does the system have a strategy to reach s in two steps? Clearly, for finite state systems, the number k of questions to ask is bounded by the number of states in the systems.

Hence, for synchronous systems, the algorithm for solving a game consists of two orthogonal parts: a routine for solving single-step games, and a "control structure" that iterates the routine. While the control structure is generally dependent only upon the specification, and indeed for some specification formalisms such as  $\mu$ -calculus, the control structure is readily obtained from the specification, the single-step games arising from different

types of synchronous systems require different solutions: for Moore systems whose outputs are independent of the current inputs, their single-step games can be solved by evaluating quantified boolean formulas (QBF) with only one  $\forall\exists$  switch: whereas for Mealy systems whose outputs may depend on the current inputs, solving the corresponding single-step games may require the evaluation of QBF formulas with multiple switches. The classification of synchronous systems and the study of their single-step games are the main theme of this dissertation.

#### 1.1.3 Games in logic and concurrency theory

Formal verification and synthesis have their roots in mathematical logic and concurrency theory, where games play an important role. We briefly mention some examples of such games which we may touch upon in this dissertation.

**Model-checking of**  $\mu$ -calculus. The model-checking problem of  $\mu$ -calculus asks, given a  $\mu$ -calculus formula  $\varphi$  and a Kripke structure K, if  $\varphi$  holds in K. The  $\mu$ -calculus model-checking problem was first studied in [EL86], and it can be casted as the *model-checking game* [Sti95].

$\mu$ -calculus Model-checking and Parity games. The exact complexity of the  $\mu$ -calculus model-checking problem remains unknown after more than a decade of active research. The best known complexity is due to [Jur00], who showed that the problem is UP  $\cap$  co-UP. It is an open problem if  $\mu$ -calculus model-checking can be done in polynomial time. On the other hand, the  $\mu$ -calculus model-checking game has been shown to be polynomially reducible to a variety of games, including parity game [Sti95, EJS93], mean payoff game [Pur95, Sti95, Jur00], discounted payoff game [ZP96] and stochastic game [Con92, Pur95, Sti95, ZP96], and the search for polynomial time solutions to these games is under active research among logicians, computer scientists and game-theorists.

Equivalence of Kripke structures. Two Kripke structures are indistinguishable by any  $\mu$ -calculus formula if and only if they are bisimilar. Bisimilarity can be characterized by the bisimilation game [Tho93. Sti97]. In essence, the bisimilation game is similar to the the Ehrenfeucht-Fraïssé game for showing elementary equivalence of first-order structures.

**Decidability of second-order logic.** To prove the decidability of the theories of monadic second order logic with n-successors (SnS). Rabin introduced what is now known as the Rabin tree automata [Rab69]. The proof entails in showing that Rabin tree automata

are closed under disjunction, projection and complementation. While proving the closure of Rabin tree automata under the disjunction and projection is relatively straight-forward, the proof of closure under complementation, also known as the Complementation Lemma, is very complicated and the original proof given by Rabin is highly involved. Many simplified proofs have been suggested [HR72, MS84, Muc84] since then. One of the best known proofs uses infinite games [GH82].

Equivalence of  $\mu$ -calculus and Rabin Tree Automata. Research on  $\mu$ -calculus gives new insight to mathematical logic. In automatic-theoretic methods, one associates, for each formula of a temporal logic, a finite automaton that recognizes exactly those infinite structures in which the formula holds. Then the satisfiability problem for the formula can be reduced to checking nonemptiness of the associated automata. When the logic is  $\mu$ -calculus, one can associate each  $\mu$ -calculus formula with a Rabin tree automaton. It has been shown that  $\mu$ -calculus on infinite trees is expressively equivalent to that of Rabin tree automata [EJ91]: given a  $\mu$ -calculus formula  $\varphi$ , there exists a Rabin tree automata U (and vice versa), such that an infinite tree U is a model of U iff U is accepted by U. Since U-calculus is trivially closed under complementation, the equivalence in expressive power provides an alternative proof of the Complementation Lemma.

Games are also used in other branches of computer science such as Finite Model Theory and Descriptive Set Theory. Note that the games used in logic and concurrency are usually turn-based (each turn either play moves) and the single-step games are trivial, whereas the games for characterizing open systems usually involve concurrent movements of the players, and hence have complicated single-step games.

#### 1.2 Thesis Overview

This dissertation studies open systems using game-theoretic means. We study the following three areas of open systems:

• Connection between open and closed systems verification: in particular, we study techniques to improve the performance of traditional model-checking using gametheoretic techniques pertaining to open systems verification. We view a system as a collection of interacting components. Each interacting component is an open system. Based on this view, we propose two novel game-theoretic verification algorithms.

namely. early error detection and automatic proof decomposition. They will be presented in Chapters 3 and 4, respectively. They are based on the materials presented in [AdAHM99, dAHM00b]. The games play on the state-space of the components and the outcome of the games are used to infer properties about the complete system; hence our algorithms fall into the category of compositional reasoning.

• Composition of synchronous open systems (systems that proceed in lock-step) and single-step control problem: a controller provides input to an open system such that the composed system behaves in a way that satisfies the specification. The output signals of the controller depends on the input and output signals of the system and some output signals of the system may not be observed. For instance, an input of the controller cannot observe an output of the system that it does not depend on. We provide game-theoretic definitions of increasingly stronger notions of input-output dependencies, or types, and show that systems equipped with the strongest type models exactly all constructive, delay-insensitive digital circuits.

We then study the problem of single-step controller synthesis (games) for systems equipped with various types and gives the complexity bounds. This will be presented in Chapter 5. Some of this material was presented in [dAHM00a, dAHM01].

• Synthesis of *uninitialized systems*: that is, open systems whose behaviors are independent of the initial states. These systems naturally presents in practical hardware, and form an interesting class of systems both practically and theoretically. We study uninitialized systems using games and the results will be presented in Chapter 6. It is based on [HKKM02].

The chapters can be read independently (except for Chapter 2 which provides all the necessary preliminaries used in all the subsequent chapters). The chapter summaries are given below.

#### 1.2.1 Early error detection in model-checking

Any formal method or tool is almost certainly more often applied in situations where the outcome is failure (a counterexample) rather than success (a correctness proof). In Chapter 3 we present a method for symbolic model-checking that can lead to significant time and memory savings for model-checking runs that fail, while occurring only a small

overhead for model-checking runs that succeed. Our method discovers an error as soon as it cannot be prevented, which can be long before it actually occurs; for example, the violation of an invariant may become unpreventable many transitions before the invariant is violated.

The key observation is that "unpreventability" is a local property of a single module: an error is unpreventable in a module state if no environment can prevent it. Therefore, unpreventability is inexpensive to compute for each module, yet can save much work in the state exploration of the global, compound system. Based on different degrees of information available about the environment, we define and implement several notions of "unpreventability," including the standard notion of uncontrollability from discrete-event control.

#### 1.2.2 Automatic assume-guarantee proof decomposition

Modular techniques for automatic verification attempt to overcome the state-explosion problem by exploiting the modular structure naturally present in many system designs. Unlike other tasks in the verification of finite-state systems, current modular techniques rely heavily on user guidance. In particular, the user is typically required to construct module abstractions that are neither too detailed as to render insufficient benefits in state exploration, nor too coarse as to invalidate the desired system properties. In Chapter 4, we propose a method where abstract modules are constructed automatically, using reachability and controllability information about the concrete modules. This allows us to leverage automatic verification techniques by applying them in layers: first we compute on the state spaces of system components, then we use the results for constructing abstractions, and finally we compute on the abstract state space of the system. Our experimental results indicate that if reachability and controllability information is used in the construction of abstractions, the resulting abstract modules are often significantly smaller than the concrete modules and can drastically reduce the space and time requirements for verification.

#### 1.2.3 The composition and control of synchronous systems

A fundamental question in the study of compositional verification of systems is the semantics of composition. Reactive systems should be non-blocking, in the sense that every state should have at least one successor state [BG88, Hal93, Kur94, Lyn96]. Non-blocking is essential for compositional techniques such as assume-guarantee reasoning. In control, non-

blocking means that the controller should never prevent the plant from moving. However in the composition of synchronous processes, non-blocking is not guaranteed in the product. For example, the composition of an inverter component  $y = \neg x$  and an identity component y = x is blocking. Blocking compositions of processes can be ruled out semantically, by insisting on the existence of certain fixed points, or syntactically, by equipping processes with types, which make the dependencies between input and output signals transparent. In Chapter 5, we classify various typing mechanisms and study their effects on the control problem. The semantics of types are given in game-theoretic terms.

A static type enforces fixed, acyclic dependencies between input and output ports. For example, synchronous hardware without combinational loops can be typed statically. A dynamic type may vary the dependencies from state to state, while maintaining acyclicity, as in level-sensitive latches. Then, two dynamically typed processes can be syntactically compatible, if all pairs of possible dependencies are compatible, or semantically compatible, if in each state the combined dependencies remain acyclic. A dependent-type resolves the dependencies gradually through a game among the components, as in gated clocks. We show that dependent-typed modules are equivalent to constructive circuits, i.e., circuits that have a constructive semantics, which are in turn equivalent to all delay-insensitive circuits.

For a given plant process and control objective, there may be a controller of a static type, or only a controller of a syntactically compatible dynamic type, or only a controller of a semantically compatible dynamic type, or only a controller of dependent-type. We show this to be a strict hierarchy of possibilities, and we present algorithms and determine the complexity of the corresponding control problems. Furthermore, we consider versions of the control problem in which the type of the controller (static, dynamic or dependent) is given. We show that the solution of these fixed-type control problems requires the evaluation of partially ordered (Henkin) quantifiers on boolean formulas, and is therefore harder (nondeterministic exponential time) than more traditional control questions. We also show that, contrary to folk wisdoms, the notion of "the most general controller" for safety properties does not exist in general for most synchronous systems.

#### 1.2.4 Synthesis of uninitialized systems

In the synthesis problem, the requirement on the input-output behavior of the synthesized system, called the stream requirement, is specified formally by modal logic formulas or  $\omega$ -automata. The Realizability Problem (RP) asks, given a stream requirement R, to find a state machine that satisfies R. The problem was first stated by Church in [Chu62], for stream requirements specified in the sequential calculus. Several solutions for it have been studied [BL69, Rab72], and in [PR89a], Pnueli and Rosner solved it for specifications given in linear temporal logic and suggested its applicability in open system synthesis and control.

In practice, however, sequential hardware is often designed to operate without prior initialization. They can be modeled by uninitialized state machines. Such machines require no reset circuitry and therefore have an advantage of smaller area. A well-known example of uninitialized state machines is the IEEE 1149.1 standard for boundary-scan test [Com90], whose specification consists of, among others, a state machine that needs not start from a known state. Uninitialized state machines are also necessary for "safe replaceability" of sequential circuits [SP94], where a state machine is replaced by another in such a way that the surrounding environment is not able to detect the changes. The replacing state machine is an uninitialized state machine because it may power-up in an arbitrary state. Uninitialized state machines have been studied by some researchers before [SP94, QBSP96]. In Chapter 6 we study the synthesis problem of uninitialized state machines.

We define the  $Uninitialized\ Realizability\ Problem\ (URP)$ , which asks given a stream requirement R on the input-output behavior, to find an uninitialized state machine M that satisfies R no matter what the initial state of M is. We study the URP for specifications that are specified by LTL formulas or Büchi automata. We consider deterministic, nondeterministic, universal, and alternating automata. In particular, we provide an algorithm for solving the URP for each of the above formalisms, and prove corresponding lower bounds. The proofs turns out to be non-trivial, and require complicated generic reductions.

# Chapter 2

# **Preliminaries**

Mathematics is a game played according to certain simple rules with meaningless marks on paper.

--- David Hilbert (1862-1943)

Let X be a set of variables. In this dissertation all variables range over the set  $\mathbb{B}$  of booleans. We denote by PStates(X) the set of partial functions from X to  $\mathbb{B}$ , and by States(X) the set of total functions. Given  $v \in PStates(X)$ , we write  $Var(v) \subseteq X$  for the set of variables on which v is defined. For  $Y \subseteq X$ , we write v[Y] for the restriction of v to the variables in Y. We indicate with  $\mathcal{P}(X)$  the set of predicates over X. For a boolean formula  $\varphi$  over X, we write  $\varphi[v] = \varphi[v(x_1)/x_1, \dots, v(x_n)/x_n]$  for the formula obtained by replacing each variable  $x_i \in Var(v)$  in  $\varphi$  with the truth value  $v(x_i)$ . If  $\varphi[v]$  contains no free variables, then we let  $\varphi[v]$  denote the truth value of  $\varphi[v]$ . We sometimes write  $v \models \varphi$  iff  $\varphi[v]$ . We write  $X' = \{x' \mid x \in X\}$  for the set of corresponding primed variables, and for  $v \in PStates(X)$ , we write v' for the partial function in PStates(X') such that v'(x') = v(x) for all  $x \in Var(v)$ , and v'(x') is undefined otherwise. Given a set A and an element x, we often write  $A \setminus X$  for  $A \setminus \{x\}$ , when this generates no confusion.

## 2.1 Modules and composition

The basic entity for modeling components of concurrent systems are modules. A module  $P = (O_P, I_P, Init_P, \tau_P)$  consists of the following three components:

• A finite set  $O_P$  of output variables. These variables are updated by the module.

- A finite set I<sub>P</sub> of input variables. These variables are updated by the environment.

The sets O<sub>P</sub> and I<sub>P</sub> must be disjoint. We write X<sub>P</sub> = O<sub>P</sub>∪I<sub>P</sub> for the set of all module variables. The states of P are S<sub>P</sub> = States(X<sub>P</sub>), and the partial (next) states of P are R<sub>P</sub> = PStates(X'<sub>P</sub>). Unprimed variables represent current-state values: primed variables, next-state values. A pair ⟨s,t'⟩ ∈ S<sub>P</sub> × R<sub>P</sub> is called an extended state. For any predicate φ ∈ P(X<sub>P</sub>), the state s ∈ S<sub>P</sub> is a φ-state if φ[s].

- An initial predicate  $Init_P \in \mathcal{P}(X_P)$ , defining the set of initial states of P.

- A boolean formula τ<sub>P</sub> ∈ P(X<sub>P</sub>∪X'<sub>P</sub>), called transition predicate, over the set X<sub>P</sub>∪X'<sub>P</sub> of variables; it relates the current-state and next-state values of the module variables. The state t∈ S<sub>P</sub> is a macro-step successor, or simply successor, of the state s∈ S<sub>P</sub> if τ<sub>P</sub>[s∪t']. For a variable x ∈ X<sub>P</sub>, the extended state ⟨s, u'⟩ ∈ S<sub>P</sub> × R<sub>P</sub> is a (micro-step) (x, τ<sub>P</sub>)-successor of the extended state ⟨s, t'⟩ if x' ∉ Var(t') and there exists b∈ B such that u' = t' ∪ {(x', b)} and τ<sub>P</sub>[s∪u'] is satisfiable.

A Moore module P is a module whose transition predicate is independent of the next-state values of the inputs, that is,  $\tau_P$  is over  $O_P \cup I_P \cup O_P'$ . Two modules P and Q are composable if their output variables  $O_P$  and  $O_Q$  are disjoint. Given two composable modules P and Q, the synchronous (lock-step) composition P||Q is the module with the components  $O_{P||Q} = O_P \cup O_Q$ ,  $I_{P||Q} = (I_P \cup I_Q) \setminus O_{P||Q}$ ,  $I_{D||Q} = (I_D \cup I_Q)$ , and  $\tau_{P||Q} = (\tau_P \wedge \tau_Q)$ .

In this dissertation, we consider modules that are non-blocking. A module P is non-blocking if it has at least one initial state, that is, the initial predicate  $Init_P$  is satisfiable: and if every state has a successor, that is, for each state s there is a state t such that  $\tau_P s \cup t'$ .

We assume that all predicates are represented in such a way that boolean operations and existential quantification of variables are efficiently computable. Likewise, we assume that satisfiability of all predicates can be checked efficiently. *Binary decision diagrams* (BDDs) provide a suitable representation [Bry86].

#### 2.2 Verification

#### 2.2.1 Specification: Linear-time temporal logic

We consider specifications expressed by linear-time temporal logic (LTL) [Pnu77] formulas over a set *Prop* of atomic propositions. The set of LTL formulas contains the atomic

15

propositions Prop, and is the smallest set closed under applications of Boolean operators, the unary temporal operator O, and the binary temporal operator U. LTL formulas are interpreted over infinite computations. A computation is a function  $\pi: N \to 2^{Prop}$ , which assigns a subset of Prop to each time instant  $i \in N$ . For a computation  $\pi = w_0, w_1, \ldots$  let  $\pi_i$  be the suffix  $w_i, w_{i+1}, \ldots$  Then we have:

- $\pi \models p \text{ for } p \in \Sigma \text{ iff } p \in w_0$ :

- $\pi \models \neg \varphi$  iff  $\pi \not\models \varphi$ :

- $\pi \models \varphi \lor \psi$  iff  $\pi \models \varphi$  and  $\pi \models \psi$ :

- $\pi \models \bigcirc \varphi$  iff  $\pi_1 \models \varphi$ : and

- $\pi \models \varphi \mathcal{U} \psi$  iff there exists  $k \geq 0$  such that  $\pi_k \models \psi$ , and for all  $0 \leq i < k$ , we have  $\pi_i \models \varphi$ .

We use the abbreviation  $\Diamond \varphi$  for  $\mathsf{T} \mathcal{U} \varphi$  which expresses the property that  $\varphi$  will eventually hold:  $\Box \varphi$  for  $\neg \Diamond \neg \varphi$  which expresses the property that  $\varphi$  always holds.

For a module P a state s of P defines a subset  $L(s) = \{x \in X_P \mid x[\![s]\!]\}$  of atomic propositions. A s-trace of P is a sequence of states  $\bar{s} = s_0, s_1, \ldots \in (S_P)^\omega$  such that  $s = s_0$  and  $\tau_P[\![s_k \cup s'_{k+1}]\!]$  for  $k \geq 0$ . A s-trace is initial iff  $Init_P[\![s]\!]$ . A s-trace induces a computation  $L(s_0)L(s_1)\ldots \in (2^{X_P})^\omega$ . Given an LTL formula  $\varphi$  over  $X_P$  and a s-trace  $\bar{s}$  of P, we say that  $\bar{s}$  satisfies  $\varphi$  if the computation induced by  $\bar{s}$  satisfies  $\varphi$ . We write  $P, s \models \varphi$  iff all s-traces of P satisfy  $\varphi$ . The LTL verification problem for a module P w.r.t. the LTL formula  $\varphi$  asks whether all initial traces of P satisfy  $\varphi$ : that is,  $P, s \models \varphi$  for all s where  $Init_P[\![s]\!]$ .

**Theorem 2.1** [AH98] The LTL verification problem for modules is PSPACE-complete.

#### 2.2.2 Reachability and invariant verification

A state of a module P is reachable if it appears in some initial trace of P. We denote by Reach(P) the predicate defining the reachable states of P: this predicate can be computed using standard state-space exploration techniques [CES86] such as Algorithm 2.1.

#### Algorithm 2.1

**Input:** Module P.

16

**Output:** Predicate Reach(P) over  $X_P$ .

Initialization: Let  $U_0 = Init_P$ .

**Repeat:** For  $k \geq 0$ . let

$$U'_{k+1} = U'_k \vee \exists X_P . (\tau \wedge U_k) .$$

Until:  $U_{k+1} \equiv U_k$ .

Return:  $U_k$ .

Algorithm 2.1 computes Reach(P) by successively computing the predicates  $U_0, U_1, \ldots, U_k = U_{k+1}$  where  $U_i$  defines the set of states that are reachable from any initial state of P in at most i steps. The predicate Reach(P) is therefore the fixpoint of the iterations, i.e.,  $U_k = U_{k+1}$ , when no more additional states can be reached.

One important LTL verification problem is the invariant verification problem which asks, given a module P and a predicate  $\varphi \in \mathcal{P}(X_P)$ , whether P satisfies the LTL formula  $\Box \varphi$ . It can be solved with the reachability predicate by checking if the implication  $Reach(P) \to \varphi$  is valid.

**Theorem 2.2** [AH98] The invariant verification problem for modules is PSPACE-complete.

#### 2.2.3 Single-step vs. multi-step verification

Consider a module P and an LTL formula  $\varphi$  over  $X_P$ . We denote by  $R(P, \varphi)$  the predicate defining the states of P that satisfy  $\varphi$ . That is, for any state  $s \in S_P$ , we have  $P, s \models \varphi$  iff  $R_P(\varphi)[\![s]\!]$ . If  $\varphi = \bigcirc \psi$ , where  $\psi \in \mathcal{P}(X_P)$ , then  $R(P, \varphi)$  can be computed by the formula

$$Pre_P(\psi) = \exists (X'_P) \cdot (\tau \wedge \psi').$$

The predicate  $Pre_P(\psi)$  is called the *predecessor* predicate, which defines the set of states that can reach a  $\psi$ -state in exactly one step. We call this the *one-step verification problem*. All other LTL verification problems can be solved by iterating, in an appropriate manner, the solutions to the the one-step verification problems [EJ91]. We call them the *multi-step* verification problems. For example, if  $\varphi = \square \psi$ , where  $\psi \in \mathcal{P}(X_P)$ , then Algorithm 2.2 computes the predicate  $R(P, \varphi)$ :

#### Algorithm 2.2

**Input:** Module P and predicate w.

**Output:** Predicate  $R(P, \Box \psi)$  over  $X_P$ .

Initialization: Let  $U_0 = \psi$ .

**Repeat:** For  $k \geq 0$ , let

$U_{k+1} = U_k \wedge Pre_P(U_k).$

Until:  $U_{k+1} \equiv U_k$ .

Return:  $U_k$ .

Algorithm 2.2 computes successively computes the sequence  $U_0, U_1, \ldots$  of stronger predicates: at the k-th iteration, predicate  $U_k$  defines the states that can stay in the set of  $\psi$ -states in at least k steps.  $R(P, \varphi)$  is therefore the conjunction of  $U_k$ , for all  $k \geq 0$ . At the core of the Algorithm 2.2 is the iteration of the predecessor predicate  $Pre_P(\varphi)$ . All other LTL formulas can also be computed in a similar fashion.

### 2.3 Controllability

We consider properties of open systems which interacts with its environment. An environment for a module P is a non-blocking module E composable with P. We can view the interaction between a module P and its environment as a game. At each round of the game, the module P chooses the next values for output variables  $O_P$ , while the environment chooses the next values for the input variables  $I_P$ . The game then continues ad infinitum. A key property of open systems is the notion of controllability: given an LTL specification  $\varphi$ , we say that a state s of P is controllable with respect to  $\varphi$  if the environment can ensure that all traces from s satisfy  $\varphi$ . For Moore modules, the above definition can be formalized using the notion of strategy. A module strategy  $\pi$  for P is a mapping  $\pi: S_P^+ \mapsto States(O_P)$ that maps each finite sequence  $s_0, s_1, \ldots, s_k$  of module states into a state  $\pi(s_0, s_1, \ldots, s_k)$ such that  $\tau_P[s_k \cup \pi'(s_0, s_1, \ldots, s_k)]$ . Similarly, an environment strategy  $\eta$  for P is a mapping  $\eta: S_P^+ \mapsto States(I_P)$  that maps each finite sequence of module states into a state specifying the next values of the input variables. Given two states  $s_1$  and  $s_2$  over two disjoint sets of variables  $X_1$  and  $X_2$ , we denote by  $s_1 \bowtie s_2$  the state over  $X_1 \cup X_2$  that agrees with  $s_1$  and  $s_2$  over the common variables. With this notation, for all  $s \in S_P$  and all module strategies  $\pi$  and environment strategies  $\eta$ , we define  $Outcome(s, \pi, \eta) \in S_P^{\omega}$  to be the trace  $s_0, s_1, s_2, \ldots$  defined by  $s_0 = s$  and by  $s_{k+1} = \pi(s_0, s_1, \ldots, s_k) \bowtie \eta(s_0, s_1, \ldots, s_k)$ . Given an LTL formula  $\varphi$  over  $X_P$ , the LTL control problem for P with respect to  $\varphi$  at a state  $s \in S_P$

18

asks if there is an environment strategy  $\eta$  such that, for every module strategy  $\pi$ , we have  $\varphi[Outcome(s,\pi,\eta)]$ . If so, then we say that a state  $s \in S_P$  is controllable with respect to  $\varphi$ . We let the controllable predicate  $Ctr(P,\varphi)$  be the predicate over  $X_P$  defining the set of states of P controllable with respect to  $\varphi$ .

**Theorem 2.3 [PR89a, AH98]** The LTL control problem for modules is 2EXPTIME-complete.

Unlike verification, the LTL control problem is easier if the LTL specification is restricted to invariants.

**Theorem 2.4 [AH98]** The invariant control problem for modules is EXPTIME-complete.

Given a module P, a state s of P and an LTL formula  $\varphi$  over  $X_P$ , we call the LTL control problem for P w.r.t.  $\varphi$  at s the one-step control problem if  $\varphi = \bigcirc \psi$  for some  $\psi \in \mathcal{P}(X_P)$ ; otherwise it is called the multi-step control problem. We let the controllable predecessor  $CPre_P(\psi)$  be the predicate over  $X_P$  defining the set of states of P controllable with respect to  $\bigcirc \psi$ . All multi-step LTL control problems can be solved by repeatedly solving the appropriate one-step control problems. For example, for the invariant specification  $\varphi = \Box \psi$ , where  $\psi \in \mathcal{P}(X_P)$  the following standard algorithm returns the predicate  $Ctr(P,\varphi)$  [TW68, Bee80, RW87]:

#### Algorithm 2.3

**Input:** Module P and predicate  $\psi$ .

**Output:** Predicate  $Ctr(P, \Box \psi)$  over  $X_P$ .

Initialization: Let  $U_0 = \psi$ .

**Repeat:** For  $k \geq 0$ . let

$U_{k+1} = U_k \wedge CPre_P(U_k).$

Until:  $U_{k+1} \equiv U_k$ .

Return:  $U_k$ .

Algorithm 2.3 computes a sequence  $U_0, U_1, U_2, \ldots$  of increasingly strong predicates. For  $k \geq 0$ , predicate  $U_k$  defines the states from which it is possible to control P to satisfy predicate p for at least k+1 steps; at each iteration  $k \geq 0$ , Algorithm 2.3 lets  $U_{k+1}$  define the set of states from which the environment can control P by ensuring that the predicate  $U_k$  is satisfied in the successor state.

If the environment of P is a Moore module, then it must decide the next value for the input variables before it can observe the next value of the output variables. Hence, to define the controllable predecessor  $CPre_{P}(p)$ , then the environment must "play first," that is,

$$CPre_P(\psi) = \exists (O'_P) \cdot \forall (I'_P) \cdot (\tau_P \to \psi')$$

The controllable predicate  $Ctr(P,\varphi)$  can also be computed by complementing the uncontrollable predicate  $UCtr(P,\varphi)$  which defines the set of uncontrollable states, that is, those states that are not controllable with respect to  $\varphi$ . The computation of  $UCtr(P,\varphi)$  involves iterating the uncontrollable predecessor  $UPre_P(\psi)$  for a predicate  $\psi \in \mathcal{P}(X_P)$ . Both  $UCtr(P,\varphi)$ and  $UPre_P(\psi)$  are defined in Chapter 3.

For general modules, and in particular for reactive modules [AH99], it is necessary to modify the definition of the controllable predicate to enable the environment to observe the next value of some output variables before choosing the next value of the input ones. More details can be found in Chapter 5. Nonethess, Algorithm 2.3 remains the same.

# Chapter 3

# Early Error Detection

Will you greet your doom

As final: set him loaves and wine: knowing

The game is finished when he plays his ace.

And overturn the table and go into the next room?

— Philip Larkin (1922–1986)

#### 3.1 Introduction

It has been argued repeatedly that the main benefit of formal methods is falsification, not verification: that formal analysis can only demonstrate the presence of errors, not their absence. The fundamental reason for this is, of course, that mathematics can be applied, inherently, only to an abstract formal model of a computing system, not to the actual artifact. Furthermore, even when a formal model is verified, the successful verification attempt is typically preceded by many iterations of unsuccessful verification attempts followed by model revisions. Therefore, in practice, every formal method and tool is much more often applied in situations where the outcome is failure (a counterexample), rather than success (a correctness proof).

Yet most optimizations in formal methods and tools are tuned towards success. For example, consider the use of BDDs and similar data structures in model checking. Because of their canonicity, BDDs are often most effective in applications that involve equivalence checking between complex boolean functions. Successful model checking is such an application: when the set of reachable states is computed by iterating image computations, successful termination is detected by an equivalence check (between the newly explored and

the previously explored states). By contrast, when model checking fails, a counterexample is detected before the image iteration terminates, and other data structures, perhaps non-canonical ones, may be more efficient [BCCZ99]. To point out a second example, much ink has been spent discussing whether "forward" or "backward" state exploration is preferable (see, e.g., [HKQ98]). If we expect to find a counterexample, then the answer seems clear but rarely practiced: the simultaneous, dove-tailed iteration of images and pre-images is likely to find the counterexample by looking at fewer states than either unidirectional method. Third, in compositional methods, the emphasis is almost invariably on how to decompose correctness proofs (see, e.g., [HQR98]), not on how to find counterexamples by looking at individual system components instead of their product. In this work, we address this third issue.

At first glance, it seems that only the least interesting of errors can be caught by looking at a single component, as the more interesting errors typically involve the interaction between multiple components. However, by precomputing information about individual components, we can detect errors that involve multiple components earlier and more efficiently than would otherwise be possible.

To explain several fine points about our method, we need to be more formal. Recall the definition of controllability of a module P in a game between P and its environment: the moves of P consist in choosing new values for the variables output by P; the moves of the environment of P consist in choosing new values for the input variables of P. A state s of P is controllable with respect to the invariant  $\Box \varphi$  if the environment has a strategy that ensures that  $\varphi$  always holds. Hence, if a state s is not controllable, we know that P from s can reach a  $\neg \varphi$ -state, regardless of how the environment behaves. The set  $C_P$ of controllable states of P can be computed iteratively, using the standard algorithm for solving safety games, which differs from backward reachability only in the definition of the pre-image operator. Symmetrically, we can compute the set  $C_Q$  of controllable states of Qw.r.t.  $\Box \varphi$ . Then, instead of checking that  $P \parallel Q$  stays within the invariant  $\Box \varphi$ , we check whether  $P \parallel Q$  stays within the stronger invariant  $\Box (C_P \land C_Q)$ . As soon as  $P \parallel Q$  reaches a state s that violates a controllability predicate, say,  $C_P$ , by retracing the computation of  $C_P$  taking into account also Q, we can construct a path of  $P \parallel Q$  from s to a state t that violates the specification  $\varphi$ . Together with a path from an initial state to s, this provides a counterexample to  $\Box \varphi$ . While the error occurs only at t, we detect it already at s, as soon as it cannot be prevented. The method can be extended to arbitrary LTL requirements.

The notion of controllability defined above is classical, but it is often not strong enough to enable the early detection of errors. To understand why, consider an invariant that relates a variable x in module P with a variable y in module Q, for example by requiring that x = y, and assume that y is an input variable to P. Consider a state s, in which module P is about to change the value of x without synchronizing this change with Q. Intuitively, it seems obvious that such a change can break the invariant, and that the state should not be considered controllable (how can Q possibly know that this is going to happen, and change the value of y correspondingly?). However, according to the classical definition of controllability, the state s is controllable: in fact, the environment has a move (changing the value of y correspondingly) to control P. This example indicates that in order to obtain stronger (and more effective) notions of controllability, we need to compute the set of controllable states by taking into account the real capabilities of the other modules composing the system. We introduce three such stronger notions of controllability: constrained, lazy, and bounded controllability. Our experimental results demonstrate that there is a distinct advantage in using these stronger notions of controllability.

Lazy controllability can be applied to systems in which all the modules are lazy. i.e., if the modules always have the option of leaving unchanged the values of their output variables [AH99]. Thus, laziness models the assumption of speed independence, and is used heavily in the modeling of asynchronous systems. If the environment is lazy, then there is no way of preventing the environment from always choosing its "stutter" move. Hence. we can strengthen the definition of controllability by requiring that the stutter strategy of the environment, rather than an arbitrary strategy, must be able to control. In the above example, the state s of module P is clearly not lazily controllable, since a change of x cannot be controlled by leaving y unchanged. Constrained controllability is a notion of controllability that can be used also when the system is not lazy. Constrained controllability takes into account, in computing the sets of controllable states, which moves are possible for the environment. To compute the set of constrainedly controllable states of a module P, we construct a transition relation that constrains the moves of the environment. This is done by automatically abstracting away from the transition relations of the other modules the variables that are not shared by P. We then define the controllable states by considering a game between P and a so constrained environment. Finally, bounded controllability is a notion that can again be applied to any system, and it generalizes both lazy and constrained controllability. It considers environments that have both a set of unavoidable moves (such as

the lazy move for lazy systems), and possible moves (by considering constraints to the moves, similarly to constrained controllability). We also introduce a technique called *iterative* strengthening, which can be used to strengthen any of these notions of controllability. In essence, it is based on the idea that a module, in order to control another module, cannot use a move that would cause it to leave its own set of controllable states.

We demonstrate the efficiency of the methods with two examples, a distributed database protocol and a wireless communication protocol. In the first example, there are two sites that can sell and buy back seats on the same airplane [BGM92]. The protocol aims at ensuring that no more seats are sold than the total available, while enabling the two sites to exchange unsold seats, in case one site wishes to sell more seats than initially allotted. The second example is from the Two-Chip Intercom (TCI) project of the Berkelev Wireless Research Center [Cen. SdSJB<sup>+</sup>00, dSJSB<sup>+</sup>00]. The TCI network is a wireless local network which allows approximately 40 remotes, one for each user, to transmit voice with point-to-point and broadcast communication. The operation of the network is coordinated by a base station, which assigns channels to the users through a TDMA scheme. In both examples, we first found errors that occurred in our initial formulation of the models, and then seeded bugs at random. Our methods succeeded in reducing the number of global image computation steps required for finding the errors, often reducing the maximum number of BDD nodes used in the verification process. The methods are particularly effective when the BDDs representing the controllable states are small in comparison to the BDD representing the set of reachable states.